𝗟𝗣𝗗𝗗𝗥𝟲 即將來到,你準備好了嗎?

沒錯,我們今天將分享的是LPDDR6 !! 雖然LPDDR5和LPDDR5x依然發展強勁,目前這些領域湧現出許多創新。但是,即使當前LPDDR5和LPDDR5x開始進入大規模生產階段,特別是LPCAMM2。領先的半導體和記憶體公司的研究人員仍在緊鑼密鼓地分析下一代技術的需求,並規劃將其融入在即將推出的LPDDR6規範中。這些公司正在JEDEC聯盟的框架內進行這項工作,Introspect Technology也是該聯盟的活躍成員之一,他們正在創建下一代低功耗記憶體規範,並應用在行動裝置到人工智慧應用等各種領域。根據最新資訊,LPDDR6的傳輸速率基本將支援10.6Gbps,甚至到達14.4Gps或更高!!

但作為專業開發者,我們都知道「變快」只是表象,背後的物理層(PHY)架構改變才是真正的挑戰。今天我們偕同Introspect,帶你快速掌握LPDDR6的三個關鍵變化與核心重點:

1️⃣全新的子通道(Sub-channels)架構

LPDDR5為了實現多通道,需要重複佈置大量的CK & CS腳位,非常佔用PCB 空間。而在LPDDR6引入了「共享訊號」概念。多個子通道可以共用一組 CK/CS訊號,這大幅減少了接腳數,讓行動裝置的空間利用率更高,但也讓訊號時序的校準變得更敏感。

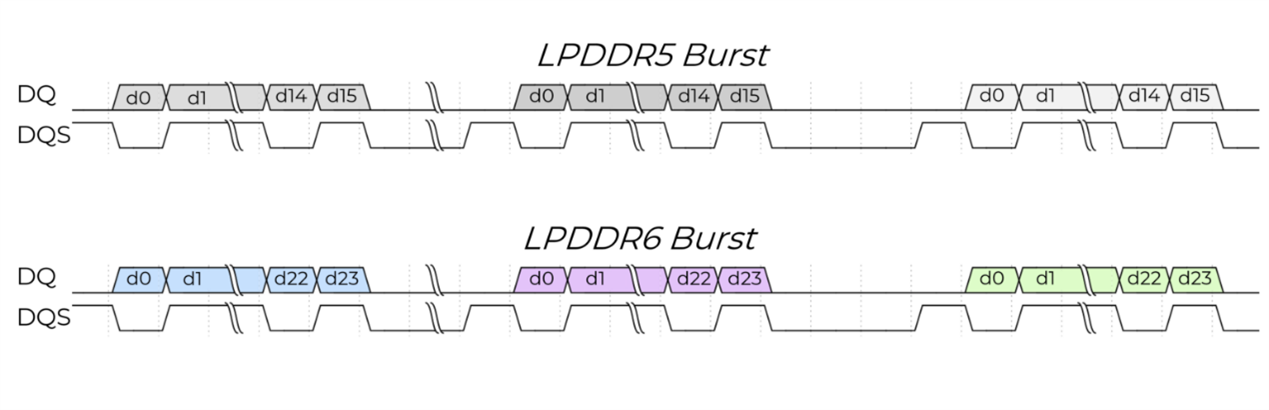

2️⃣24-bit Burst Length

LPDDR5常用的是BL16,而LPDDR6躍升到了 BL24。這代表每一次傳輸能攜帶更多資訊。有趣的是,這24 bits裡不僅包含資料,還預留了空間給錯誤校正(ECC)與安全機制。這確保了在極高頻率下,資料傳輸依然能維持極低的錯誤率。

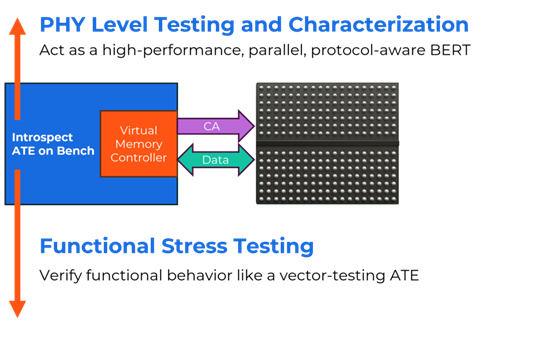

3️⃣驗證難度翻倍

當頻率破10Gbps,傳統的示波器量測已經無法完全解決問題。未來的測試重點將轉向Protocol-aware BERT。測試設備必須能像「模擬 CPU」一樣,自動跟記憶體進行Training,才能在真實運作的情境下找出潛在的Rx & Tx弱點。

LPDDR6的標準定義了未來五年的行動運算規格。如果您正身處晶片設計或系統整合的第一線,現在就是重新評估測試方案的最佳時機。

點擊查看完整原文: LPDDR6 Is Coming: Are You Ready?

誠芯技術陪你洞見未來