複雜測試環境中的PCIe訊號連接藝術

構建大規模測試矩陣:PCIe 擴展與訊號扇出技術解析

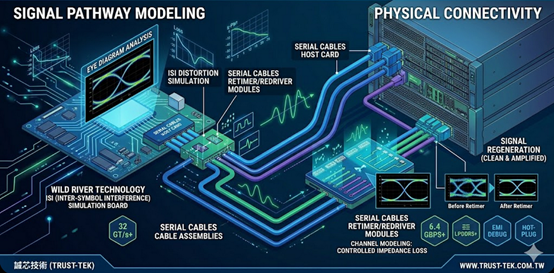

隨著PCIe邁入Gen5 (32 GT/s)甚至Gen6 (64 GT/s)的PAM4時代,訊號容許誤差(Loss Budget)已縮減至極限。在開發測試環境中,任何一段Cable Assembly(連接纜線)或NIC、GPU等主機板上的子卡片的阻抗不連續,都會導致眼圖閉合。工程師面臨的最大挑戰,是如何在「極長走線」與「多節點擴展」的現實環境下,依然維持訊號的完整度?

根據Wild River Technology在高速通道建模(Channel Modeling)領域的洞察,量測的準確性建立在「可追溯的損耗」之上。領先的驗證團隊會使用ISI模擬板,在實驗室中精確模擬不同長度的PCB走線損耗。這種作法讓工程師在接入真實設備前,能先建立一套基準通道模型。透過這種「受控的雜訊與損耗」,我們可以驗證系統在最惡劣通道條件下的容忍極限。

然而,當模擬完成,進入真實的大規模測試架構時,物理連接的品質就成了決定性因素。Serial Cables提供的專業級Host Card與Cable Assembly,設計核心即在於極低的插入損耗(Insertion Loss)與回波損耗(Return Loss)。但在超長距離的扇出(Fan-out)應用中,單靠被動線材已不足以克服衰減,這時 Retimer與Redriver技術的導入便顯得至關重要。

Retimer能在物理層重新物理化(Re-time)訊號,徹底消除累積的Jitter,而Redriver則透過等化技術(Equalization)補償通道損耗。在複雜的伺服器測試矩陣中,將Serial Cables的Retimer擴展板與Wild River Technology的訊號模型板結合,能構建出一套既具備大規模擴展能力,又能維持「準確量測等級」的測試鏈路。這種從通道模擬到主動訊號補償的整合方案,已成為解決 PCIe高頻訊號衰減、確保Bit Error Rate(BER)達標的工業級標準路徑。