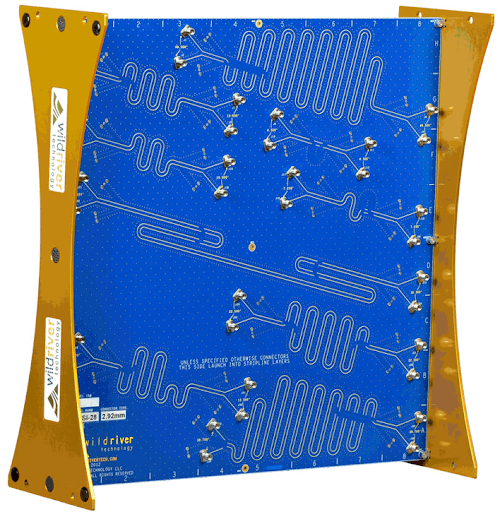

Wild river technology的channel-modeling / loss-modeling平台,例如ISI-56、ISI-112、 ISI-224等就是在這種「設計瓶頸」前,給設計者一台能「預先模擬真實世界通道行為」的工具。這系列平台是針對SERDES/PAM-4 & NRZ系統,為56Gbps到224 Gbaud 傳輸打造的loss-platform。它不是用假設性的 stub、共振器或人為模擬,而是真正用「介電材料損耗(dielectric loss)、金屬導體損耗(conductor loss)、趨膚效應(skin effect)」這些物理現象來造成訊號衰減與失真。也就是說,當你把你的發射器(TX)/接收器(RX)接在這個平台上,所看到的loss、ISI、jitter都是非常真實且可重複的,完全模擬真實PCB、走線、連接器、灌孔、阻抗變化等在高速環境下會產生的影響。

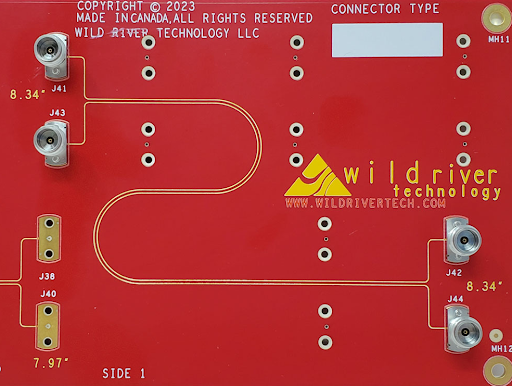

不管是用於PCIe、SerDes、USB4、資料中心背板,或是任何需要在高傳輸速率/高頻寬下傳輸資料的系統。隨著傳輸速率往上衝,訊號完整性(signal integrity, SI)變成關鍵,一點微小的不連續、材料不均、走線瑕疵、接頭誤差,就可能造成訊號衰減(loss)、符號間干擾(ISI)、群延遲變異(group-delay skew)、回波(reflection)、串擾(crosstalk),這些問題會讓接收端的均衡(equalization) 變得非常敏感,也讓系統於量產/實際運作中常出問題。這套平台由多條不同長度的差分訊號組成,你可以依據需要選擇插入損失量 (insertion loss),在56 GHz時,損耗可以從 –8 dB到 –28 dB、每次以1 dB來調整。對應到真實設計中可能的最差情況,背板長度、材料特性、走線密度、灌孔數量與布局複雜性,為工程師準備了一個非常有彈性的模擬環境。

重點是,使用這樣的channel-loss平台,可以讓你在還沒做實體PCB/背板之前,就先驗證你的SERDES設計/equalization/時序設定是否足夠安全。也就是說,你不必打板就能知道在「理論極限+真實loss + worst-case layout」條件下,信號能不能穩定通過、眼圖會不會變形、接收端能不能正確解碼。對於要支援高速通道、高密度背板、緊湊布局、甚至是多通道系統來說,這是一個大幅降低風險的關鍵工具,也讓你省去打版後再事後修改、重測還來得更有效率。